首页 > bsport体育注册

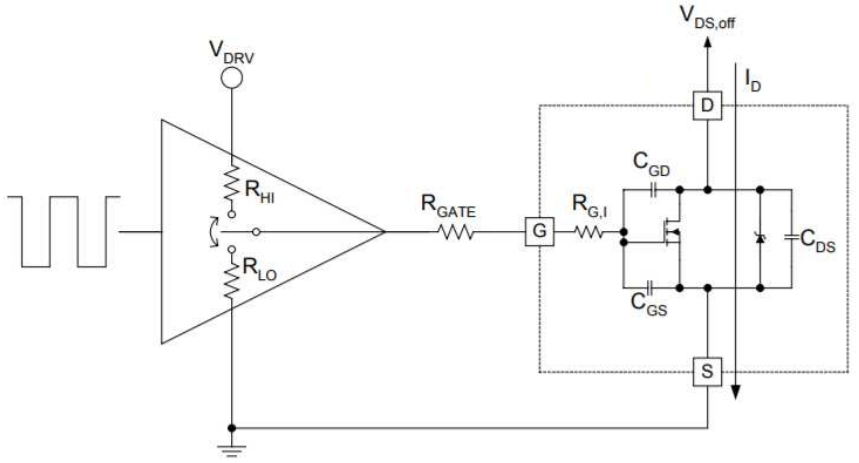

器的等效电路来计算如何合理的选取RGATE电阻的阻值,既要保持MOS管的良好开关性能,还要有效抑制振铃的产生。通过计算后的理论值来实验,能够最大化的选取合理的RGATE阻值。另外针对栅极驱动回路中,导通和关断回路进行了不同的结构形态的计算,来研究有无串联带来的影响,同时针对三种结构的电路进行功耗计算,最后文章中给出低侧栅极驱动器Layout中的注意事项,还有不同

以上参数中,RLO可以通过查阅datasheet直接得到,由于驱动芯片内部是NMOS和PMOS并联混合上拉结构,所以在计算中RHI≈RLO *1.5;MOSFET内部的RG,I可以通过查阅datasheet得到,如果规格书内未注明RG,I可使用LCR电桥在GS两端施加1MHz的测试信号,测得Rs值即为RG,I。

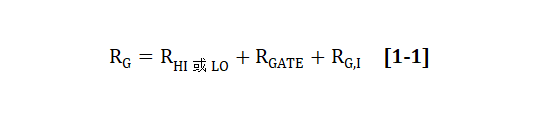

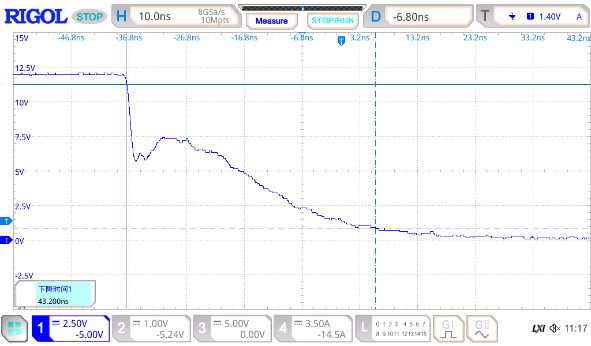

图1-1展示了实际电路中的谐振回路,寄生电感LS和输入电容GISS产生高频谐振,而RG则是起到衰减谐振的作用,Q为阻尼系数,一般取0.5。

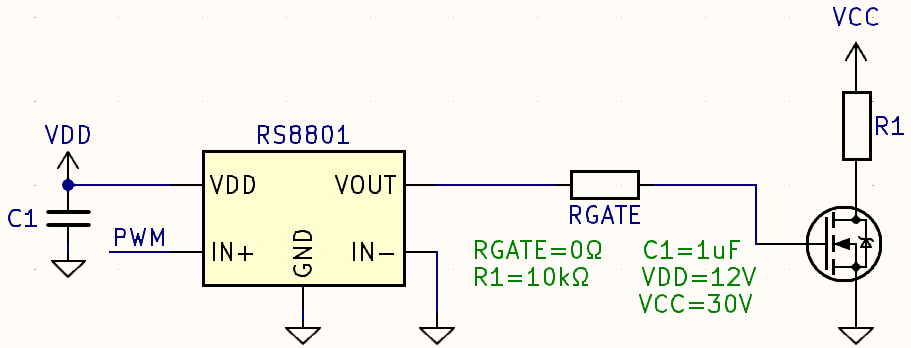

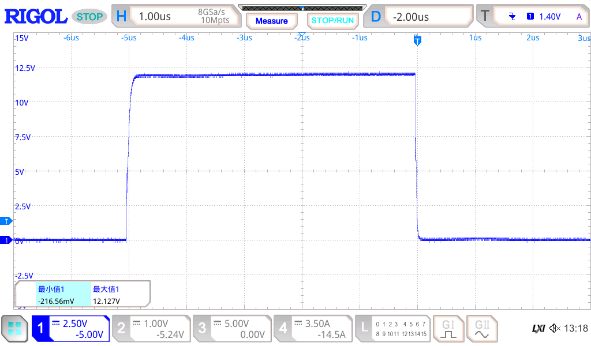

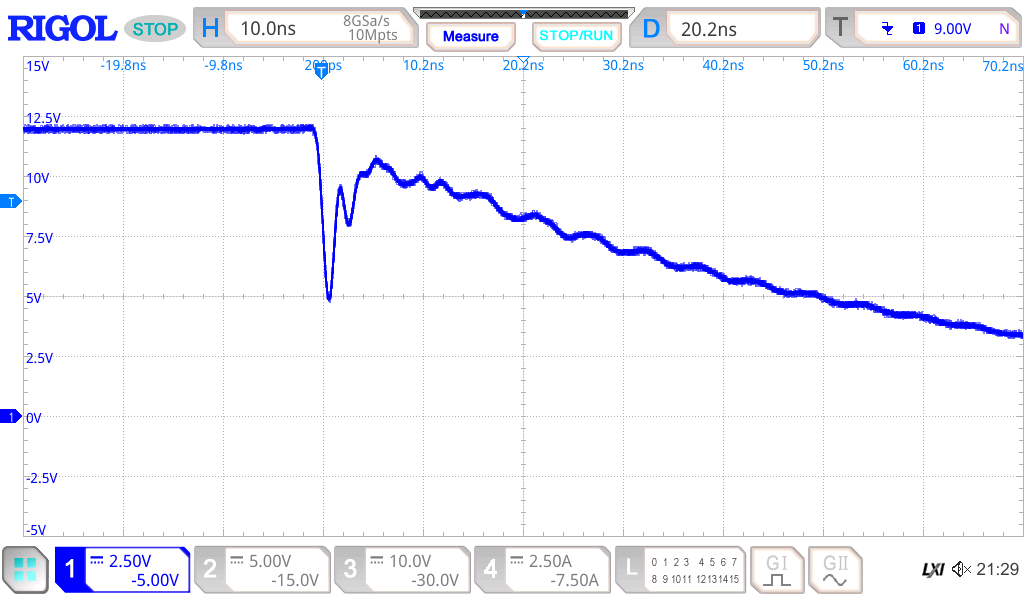

使用RS8801驱动MOS-IRFB3607,外部栅极电阻RGATE取0Ω进行初步实验,使用探头x10档、接地弹簧得到以下波形:

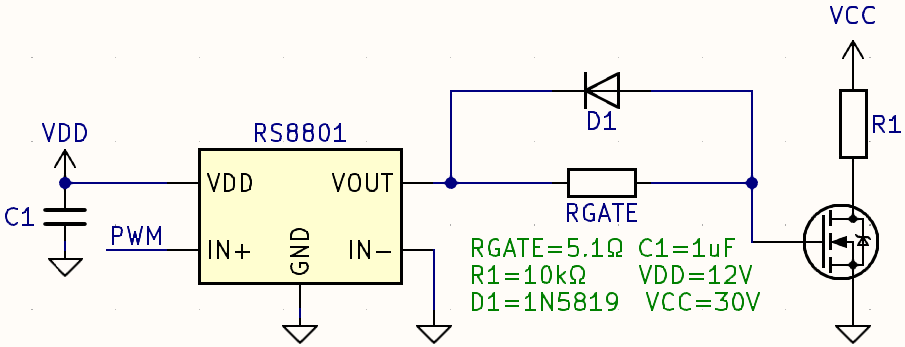

驱动MOS需要遵守 “慢开快关“的原则 ,慢开是指MOS管开通时不能因驱动波形振荡而引起EMI问题,快关则是指MOS管关断要尽可能的快,一方面可以减小关断损耗,另一方面在半桥驱动的场合保证死区时间,防止炸管。但是前文中RGATE阻值已经确定,如何才能做到不改变RGATE的情况下快速关断MOS呢?见下图2-1

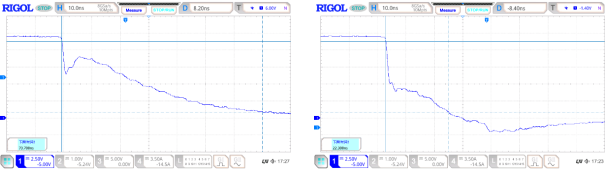

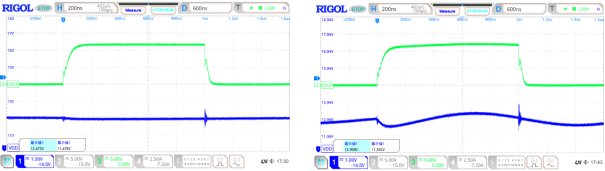

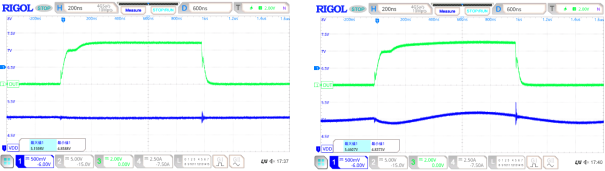

左图是没有D1的关断波形,下降沿大约70nS,右图是加了快速关断二极管D1的关断波形,下降沿约为22nS,可以看到D1的效果十分明显。

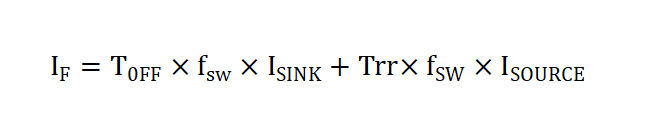

D1的选型需要关注Trr(反向恢复时间)、开关频率这两个参数,为了不影响开通时的电流路径我们希望Trr越小越好,同时二极管最大开关频率也要匹配开关管的工作频率,所以低Trr、高开关频率的肖特基二极管(Trr一般在10nS左右,频率可以上GHz)十分适用于此应用场合。

但是这又引入了一个新的问题:关断时的电流直接通过二极管而不经过电阻进入驱动器,相较于不加二极管的电路,会让芯片关断时功耗增加,从而提高整个开关周期内的功耗。

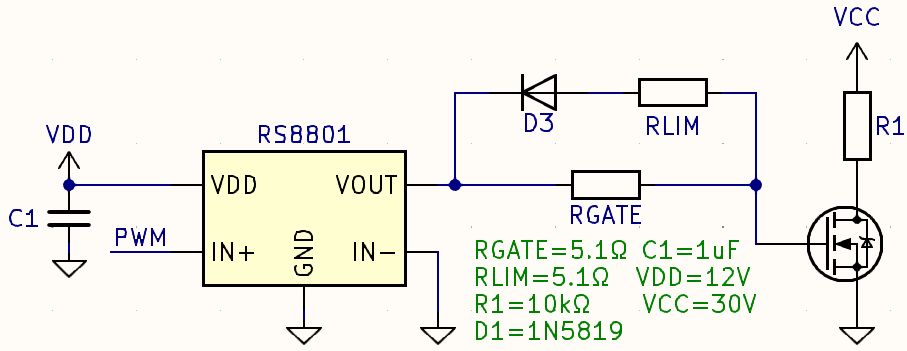

图2-3的电路在二极管端增加了一个5.1Ω限流电阻,这样可以减小关断期间驱动器的功耗,从而降低驱动器整体功耗,但是在降低功耗的同时也降低了关断速度(见下图),如果想加快关断速度,可以将限流电阻继续减小。

栅极驱动芯片工作时产生的高速脉冲需要从VDD电容汲取能量,规格书中推荐电容取值1uF,考虑到很多客户可能会习惯性的取100nF作为滤波电容,故以图2-5电路做以下实验(PWM=300kHz):

从绿色的OUT波形来看,两种容值效果接近,但从是蓝色波形可以看到使用100nF时,VDD电压波动较大,考虑到芯片的UVLO-OFF阈值电压约为4V,在供电较低的应用中需要关注VDD电压的波动不能触及UVLO-OFF阈值电压。

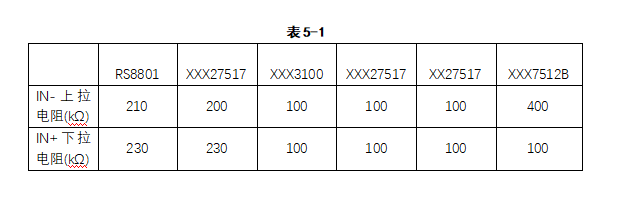

许多工程师喜欢在上下拉的引脚中串联一个电阻后接到电源或地,但是对于RS8801却不建议这么做,原因是芯片内部上下拉电阻为200kΩ,如果在外部串接电阻会使得引脚上产生分压,可能引起电路工作异常。

从这个案例可以看到一旦外置上下拉电阻取值不合理,就会引起整个电路工作异常,因此建议上下拉的时候不要串联电阻。但是当使用一个信号控制多片RS8801时,三极管(或MOS管)的下拉电阻是必须的,所以遇到这种应用更要重点检查阻值选取是否合理。

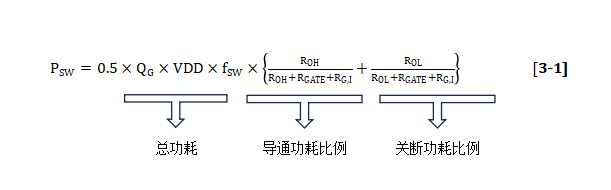

以图1-2的电路为例:ROL=0.5Ω 、ROH=1.5*ROL=0.75Ω 、RGATE=5.1Ω 、RG,I=0.55Ω、VDD=12V、

则芯片功耗为0.025W,随后计算RGATE功耗的时候只需要将两项功耗比例的分子改为RGATE的阻值,可得RGATE功耗为0.2W,此时芯片功耗较低,但是RGATE功耗很大,至少要选取1206封装,如果想减小RGATE封装,可适当增大其阻值。

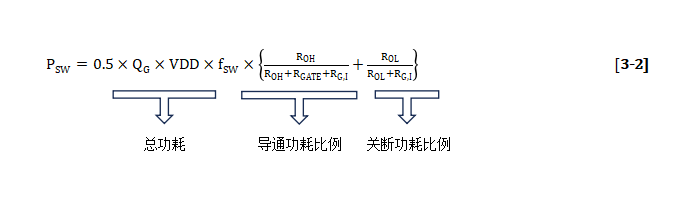

以图2-1的电路为例:ROL=0.5Ω 、ROH=1.5*ROL=0.75Ω 、RGATE=5.1Ω 、RG,I=0.55Ω、VDD=12V、QG≈70nC;假设fsw=300kHz。

以图2-3的电路为例:ROL=0.5Ω 、ROH=1.5*ROL=0.75Ω、RGATE=5.1Ω 、RG,I=0.55Ω、RLIM=5.1Ω、VDD=12V、QG≈70nC;假设

开关管输入电容下端驱动器下管RGATE开关管输入电容上端输入电容下端即开关管的地,驱动器下管即驱动器的地,这两个地之间的寄生电感会引起驱动器OUT端产生负压,从而引起驱动器失效,所以Layout的时候不光要关注输出线,回流地线、替代料的关注点

从上述两个品牌芯片调试案例来看,增大RGATE似乎是最简单有效的,但为了稳定波形去掉了加速关断二极管,使整个关断周期超过150nS,这增加了关断损耗,所以说增大RGATE是一把双刃剑。

对处于新设计阶段的客户,建议在外部上下拉的电路中不要串联电阻,因为各个品牌芯片的内置上下拉电阻阻值各不相同,可能会出现替代后无法正常工作的情况。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。举报投诉

是每个器件的电气隔离控制端。MOSFET的另外两端是源极和漏极,而对于IGBT,它们被称为集电极

发生了什么,手册也没有说明这一点。根据手册,必须首先通过将 F0 或 F1(或两者)置为高电平来启用

源连接(R57、R58 和 R59)中也有 4R7 电阻,我不明白为什么需要这些。是否有任何设计

(一) /

【米尔-全志T113-i开发板试用】发布opencv-mobile米尔t113i专享预编译包

询价